SANTA CLARA, USA: SiliconBlue Technologies, the leading supplier of ultra-low power, single-chip SRAM FPGAs, recently announced that Siltrontech Electronics Corp. has been selected as a distributor for mainland China and Taiwan.

Established in 1992, Siltrontech will provide sales and technical support for SiliconBlue’s ultra-low power, single-chip iCE65 mobileFPGAs targeted at the rapidly-growing consumer handheld market.

"Siltrontech’s experience selling and supporting products for the mobile communications market is a great benefit to SiliconBlue as we expand our sales force in mainland China and Taiwan," said Kapil Shankar, CEO of SiliconBlue. "We are delighted to have a world class distributor selling and supporting our ultra-low power FPGAs in such an important market."

"SiliconBlue offers the most innovative FPGAs perfectly suited to our customer’s requirements," said Tony Chou, President at Siltrontech. "The iCE65 FPGA is an excellent addition to our product line, and provides an exciting new alternative to consumer hand-held designers who need the benefits of ultra-low power, single-chip, low-cost, constrained space and fast time-to-market for applications such as mobile phones, MIDs, eBooks, netbooks and digital picture frames."

iCE65 family of FPGAs

iCE65 ultra-low power FPGAs are the premier programmable logic solution for consumer, battery-based applications such as smart phones, eBooks/ePaper, netbooks, digital picture frames, mobile internet devices, portable media players, handheld POS, medical instruments, digital still cameras and flash camcorders.

These applications have an extremely short development and product life cycle; therefore, by combining the reprogramming flexibility benefit of FPGAs with the low cost, low power and single-chip benefits of ASICs, iCE65 FPGAs offer the “best of both worlds” solution for handheld consumer system designers.

Sunday, May 31, 2009

TES reinforces position in telematics device market

LANGON, FRANCE:TES Electronic Solutions, a leader in electronic design and manufacturing services, recently unveiled its latest initiative in the telematics market; a reference device called TITAN that can be quickly customised and tailored to address the majority of Telematics Service Providers requirements.

TES is leveraging its complete service breadth of electronic design and manufacturing together with its vast experience in RF and positioning technologies to the specific segment of telematics devices. The TITAN platform is the first of a range of reference platforms.

It is available in two configurations; a thin client device running Linux or Windows CE or as a low cost M2M platform. All reference designs and devices provide GPS, GSM/GPRS and basic but highly configurable I/O, while the thin client device offers an ARM 9 processor in addition to enable application deployment on the device.

The reference platform strategy is complemented with TES Electronic Solutions’ extensive design team to provide tailored telematics hardware and software solutions which can be rapidly moved into volume manufacturing in TES factories. Once in volume supply, customers can further benefit from TES’ logistics platform for device configuration and distribution to installation centres.

“In addition to applications that track vehicles and capital equipment, we are seeing new areas emerging such Pay As You Drive, Pay How You Drive and Pay When You Drive”, said Nick Walker, Senior Vice President of Business Development at TES. “Every application is different and needs optimised hardware and software in this rapidly growing and competitive market”, continued Walker.

“TES Electronic Solutions have all the skills and expertise to create, design, manufacture and distribute optimised telematics devices for every application. It’s a custom business where one size does not fit all, but all require a common set of basic functions. Our approach to the business is geared to allow the telematics service providers to focus on building out the applications based on the device while we take care of the device delivery”, he concluded.

Available now, the TITAN reference device is fitted with a Telit quad band modem including SiRF StarIII GPS that provides the communications and positioning technology, which can operate standalone for simple cost optimised applications. In the top end configuration, TITAN also includes an ARM 9 processor module for the OS and application for the more sophisticated telematics application.

The TITAN device is the first step in an emerging telematics strategy from TES. Further announcements will be made in the coming weeks.

TES is leveraging its complete service breadth of electronic design and manufacturing together with its vast experience in RF and positioning technologies to the specific segment of telematics devices. The TITAN platform is the first of a range of reference platforms.

It is available in two configurations; a thin client device running Linux or Windows CE or as a low cost M2M platform. All reference designs and devices provide GPS, GSM/GPRS and basic but highly configurable I/O, while the thin client device offers an ARM 9 processor in addition to enable application deployment on the device.

The reference platform strategy is complemented with TES Electronic Solutions’ extensive design team to provide tailored telematics hardware and software solutions which can be rapidly moved into volume manufacturing in TES factories. Once in volume supply, customers can further benefit from TES’ logistics platform for device configuration and distribution to installation centres.

“In addition to applications that track vehicles and capital equipment, we are seeing new areas emerging such Pay As You Drive, Pay How You Drive and Pay When You Drive”, said Nick Walker, Senior Vice President of Business Development at TES. “Every application is different and needs optimised hardware and software in this rapidly growing and competitive market”, continued Walker.

“TES Electronic Solutions have all the skills and expertise to create, design, manufacture and distribute optimised telematics devices for every application. It’s a custom business where one size does not fit all, but all require a common set of basic functions. Our approach to the business is geared to allow the telematics service providers to focus on building out the applications based on the device while we take care of the device delivery”, he concluded.

Available now, the TITAN reference device is fitted with a Telit quad band modem including SiRF StarIII GPS that provides the communications and positioning technology, which can operate standalone for simple cost optimised applications. In the top end configuration, TITAN also includes an ARM 9 processor module for the OS and application for the more sophisticated telematics application.

The TITAN device is the first step in an emerging telematics strategy from TES. Further announcements will be made in the coming weeks.

Saturday, May 30, 2009

Accelerometers set to become leading MEMS device in 2013

EL SEGUNDO, USA: When you turn your iPhone to the side and the screen automatically adjusts from portrait to landscape view, there’s an accelerometer at work. When you swing your Wii controller and bowl a virtual strike, there’s an accelerometer at work.

Indeed, accelerometers in recent years have emerged as a critical input device for some of the world’s hottest electronic products, causing shipments to boom. This will make accelerometers the top-selling Microelectromechanical System (MEMS) device by 2013, according to iSuppli Corp.

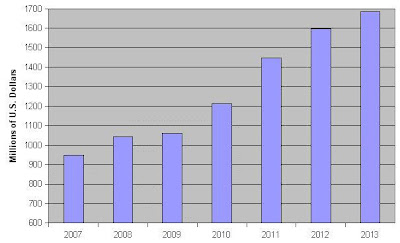

The global MEMS accelerometer market will expand to $1.7 billion in 2013, up from $947.7 million in 2007, as presented in the figure. Source: iSuppli

Source: iSuppli

“Due to this rapid sales growth, accelerometers by 2013 will displace the current leading MEMS products—inkjet heads and Digital Light Processing (DLP) chips—to become the dominant type of MEMS device sold worldwide in 2013,” said Jérémie Bouchaud, principal analyst, MEMS, for iSuppli. “Consumers’ desire for motion-sensing in smart phones and video game systems will boost demand for accelerometers.”

The boom in accelerometer demand will come as a boon to the health of the overall MEMS market. Although global MEMS revenue will decline by 8 percent in 2009—the second decline in market history following a 7 percent decrease in 2008—accelerometers will still manage 1.8 percent growth. Accelerometer revenue will rise by 14.1 percent in 2010 and will maintain double-digit percentage growth in 2011 and 2012.

“A major catalyst for the rise in accelerometer sales is pricing,” Bouchaud noted. “Accelerometers broke the magic $1 barrier in 2008, making them attractive in a larger number of products. Their prices will continue to decline in the coming years, widening their appeal beyond smart phones to reach the wider mobile handset market.”

In 2009, revenue from consumer and mobile applications for accelerometers is expected to exceed that of automotive applications. Until now, Automotive has been the biggest application by far for accelerometers, but this area now is suffering from the global collapse of car production.

Automotive applications accounted for 40 percent of global accelerometer revenue in 2008, down from 78 percent in 2006. In contrast, consumer electronics and wireless accelerometer revenue rose from 22 percent to 58 percent during the same period.

STMicroelectronics rides consumer wave to top of accelerometer market

In 2006, the top five accelerometer suppliers -- Freescale, Analog Devices, Bosch, VTI and Denso -- almost exclusively served the automotive market. However, by the end of 2008, STMicroelectronics had taken the lead in accelerometers based on its significant success in supplying the burgeoning consumer and wireless communications markets.

STMicroelectronics’ global accelerometer revenue rose to $220 million in 2008, up by nearly a factor of eight from $29 million in 2007. The company’s accelerometer market share rose to 20 percent in 2008, up from 4 percent in 2006.

Indeed, accelerometers in recent years have emerged as a critical input device for some of the world’s hottest electronic products, causing shipments to boom. This will make accelerometers the top-selling Microelectromechanical System (MEMS) device by 2013, according to iSuppli Corp.

The global MEMS accelerometer market will expand to $1.7 billion in 2013, up from $947.7 million in 2007, as presented in the figure.

“Due to this rapid sales growth, accelerometers by 2013 will displace the current leading MEMS products—inkjet heads and Digital Light Processing (DLP) chips—to become the dominant type of MEMS device sold worldwide in 2013,” said Jérémie Bouchaud, principal analyst, MEMS, for iSuppli. “Consumers’ desire for motion-sensing in smart phones and video game systems will boost demand for accelerometers.”

The boom in accelerometer demand will come as a boon to the health of the overall MEMS market. Although global MEMS revenue will decline by 8 percent in 2009—the second decline in market history following a 7 percent decrease in 2008—accelerometers will still manage 1.8 percent growth. Accelerometer revenue will rise by 14.1 percent in 2010 and will maintain double-digit percentage growth in 2011 and 2012.

“A major catalyst for the rise in accelerometer sales is pricing,” Bouchaud noted. “Accelerometers broke the magic $1 barrier in 2008, making them attractive in a larger number of products. Their prices will continue to decline in the coming years, widening their appeal beyond smart phones to reach the wider mobile handset market.”

In 2009, revenue from consumer and mobile applications for accelerometers is expected to exceed that of automotive applications. Until now, Automotive has been the biggest application by far for accelerometers, but this area now is suffering from the global collapse of car production.

Automotive applications accounted for 40 percent of global accelerometer revenue in 2008, down from 78 percent in 2006. In contrast, consumer electronics and wireless accelerometer revenue rose from 22 percent to 58 percent during the same period.

STMicroelectronics rides consumer wave to top of accelerometer market

In 2006, the top five accelerometer suppliers -- Freescale, Analog Devices, Bosch, VTI and Denso -- almost exclusively served the automotive market. However, by the end of 2008, STMicroelectronics had taken the lead in accelerometers based on its significant success in supplying the burgeoning consumer and wireless communications markets.

STMicroelectronics’ global accelerometer revenue rose to $220 million in 2008, up by nearly a factor of eight from $29 million in 2007. The company’s accelerometer market share rose to 20 percent in 2008, up from 4 percent in 2006.

Labels:

accelerometers,

Analog Devices,

Bosch,

Denso,

Freescale,

iPhone,

iSuppli,

MEMS,

MEMS accelerometers,

MEMS devices,

Nintendo Wii,

ST,

VTI

GSA appoints Neil Kim as new director

SAN JOSE, USA: Global Semiconductor Alliance (GSA), the platform for global collaboration, announces its most recent addition to the board of directors, Neil Kim, Senior Vice President of Operations and Central Engineering at Broadcom Corporation.

At Broadcom, Kim is responsible for all global manufacturing activities, including foundry operation, packaging and test engineering as well as setting the process technology direction. Additionally, he is responsible for engineering activities that include the development of analog mixed-signal and radio frequency (RF) products and building Broadcom's library of core technologies.

He joined Broadcom as director of engineering in January 2000 and became vice president of central engineering in October 2001.

Prior to joining Broadcom, Kim held a series of progressively senior technical and management positions at Western Digital Corporation, where his last position was vice president of engineering. He received a B.S.E.E. from the University of California, Berkeley.

In his position at Broadcom, Kim manages the company’s vital relationships with its foundries and assembly and test suppliers.

Moreover, his extensive knowledge in analog mixed-signal and RF products brings value to GSA by enabling a better understanding of the complexity involved in managing the analog mixed-signal and RF product deliverables. His addition to the GSA board of directors will enhance its diversity and improve the Alliance’s ability to service the global supply-chain.

“I appreciate this appointment by the board and look forward to working with my peers, partners and competitors to bring about a more efficient ecosystem so that we all benefit. GSA is an exceptional organization in that it identifies challenges and opportunities and achieves maximum value for the industry,” stated Neil Kim.

Broadcom, a GSA member since 1998, is a major technology innovator and global leader in semiconductors for wired and wireless communications. Broadcom products enable the delivery of voice, video, data and multimedia to and throughout the home, the office and the mobile environment. “Broadcom has been a great supporter of GSA over the life of the Alliance. They have established themselves as a role and success model for the semiconductor community. We are pleased that Neil Kim will represent them on our board of directors,” said Jodi Shelton, president of GSA.

“Neil’s broad knowledge and experience provides an additional perspective of managing a multifaceted supply chain and understanding the challenges that companies face. This will further develop our ability to facilitate and drive solutions to the industry. It is our ambition to learn and grow from experts like Kim. His contribution will be of great benefit to GSA’s continued success,” Shelton further commented.

The GSA board of directors is comprised of 25 industry executives representing all sectors of the semiconductor industry and includes all geographies and representatives from critical supply partners.

At Broadcom, Kim is responsible for all global manufacturing activities, including foundry operation, packaging and test engineering as well as setting the process technology direction. Additionally, he is responsible for engineering activities that include the development of analog mixed-signal and radio frequency (RF) products and building Broadcom's library of core technologies.

He joined Broadcom as director of engineering in January 2000 and became vice president of central engineering in October 2001.

Prior to joining Broadcom, Kim held a series of progressively senior technical and management positions at Western Digital Corporation, where his last position was vice president of engineering. He received a B.S.E.E. from the University of California, Berkeley.

In his position at Broadcom, Kim manages the company’s vital relationships with its foundries and assembly and test suppliers.

Moreover, his extensive knowledge in analog mixed-signal and RF products brings value to GSA by enabling a better understanding of the complexity involved in managing the analog mixed-signal and RF product deliverables. His addition to the GSA board of directors will enhance its diversity and improve the Alliance’s ability to service the global supply-chain.

“I appreciate this appointment by the board and look forward to working with my peers, partners and competitors to bring about a more efficient ecosystem so that we all benefit. GSA is an exceptional organization in that it identifies challenges and opportunities and achieves maximum value for the industry,” stated Neil Kim.

Broadcom, a GSA member since 1998, is a major technology innovator and global leader in semiconductors for wired and wireless communications. Broadcom products enable the delivery of voice, video, data and multimedia to and throughout the home, the office and the mobile environment. “Broadcom has been a great supporter of GSA over the life of the Alliance. They have established themselves as a role and success model for the semiconductor community. We are pleased that Neil Kim will represent them on our board of directors,” said Jodi Shelton, president of GSA.

“Neil’s broad knowledge and experience provides an additional perspective of managing a multifaceted supply chain and understanding the challenges that companies face. This will further develop our ability to facilitate and drive solutions to the industry. It is our ambition to learn and grow from experts like Kim. His contribution will be of great benefit to GSA’s continued success,” Shelton further commented.

The GSA board of directors is comprised of 25 industry executives representing all sectors of the semiconductor industry and includes all geographies and representatives from critical supply partners.

Labels:

Broadcom,

Global Semiconductor Alliance,

GSA,

Neil Kim

Friday, May 29, 2009

IC Validator offers step up in physical designer's productivity

Recently, Synopsys Inc. introduced an IC Validator design rule checking/layout verification signoff (DRC/LVS) for in-design physical verification and signoff for advanced designs at 45nm and below.

Said to provide a step up in physical designer productivity, it is architected to deliver the high accuracy necessary for leading-edge process nodes, superior scalability for efficient utilization of available hardware, and ease-of-use.

What does IC Validator do?

According to Sanjay Bali, Director of Marketing, Physical Verification & DFM, Synopsys, the IC Validator is a complete physical verification tool, performing increasingly complex DRC and LVS sign-off checks.

It has been specifically architected for in-design physical verification. This means: the place-and-route engineers can run DRC and practical DFM steps alongside place and route within the familiar IC Compiler physical design environment.

And, why need for such a solution? He added that three key summary challenges are driving the need for a new approach and hence the new tool. These are:

a) Increase in complexity and count of manufacturing rules.

b) Unabated growth on design complexity.

c) Increasing DFM challenges, which just cannot be handled in a post processing approach.

Currently, the solution is aimed at 45nm and below as these nodes largely represent the challenges listed above.

Enhancing physical designer's productivity

Three key tenants of the IC Validator that offer improved physical designer productivity are:

a) High accuracy necessary for leading-edge process nodes.

b) Superior scalability for efficient utilization of available hardware. And,

c) Ease of use with seamless integration of IC Validator and IC Compiler

Bali said: "The IC Validator has been architected from the ground up for in-design physical verification. In-design physical verification enables place-and-route engineers to accelerate the time to tapeout by enabling sign-off quality physical verification from within implementation or physical design. Physical designers designing with IC Compiler can now benefit from the in-design physical verification approach with the push of a button, incurring minimal overhead cost to eliminate surprises late in the design.

"With the verify-as-you-go approach replacing the implement-then-verify approach, physical designers can significantly reduce iteration count, eliminate streamouts and streamins, and accelerate time to tapeout. In addition, the integration enables several productivity enhancing flows like incremental DRC verification, incremental metal fill flows and ECO flows -- all leading to significant reduction in time to tapeout."

It would be interesting to determine or know by approximately what percent is the total physical verification time reduced, and what all does it cover in the process?

Bali added that in extreme cases, finding and fixing DRC violations can easily impact the schedules by a few weeks! The key here is that physical designers typically wait until the final stages of the tapeout to run physical verification. Inevitably, the schedule at this point is squeezed and the cost of fixing the error is high.

"With a sign-off quality physical verification tool integrated into the physical design environment, place-and-route engineers can verify as they implement and eliminate late surprises while speeding up the total physical verification turnaround time. In addition, the outcome of this process is a sign-off clean design.

Production ready!

The Synopsys IC Validator is also said to 'production ready!" What exactly does that mean?

The IC Validator has been successfully used to tapeout designs at several chip manufacturers, said Bali. In addition, it is currently being used for production designs at Nvidia and Toshiba. Besides other leading foundry's and chip manufactures it is also qualified by TSMC for 40nm and 28nm process nodes.

For those interested, Toshiba already has Synopsys as its key EDA partner, and NVIDIA adopted the IC Validator for sign-off physical verification, within days of its launch! More are bound to follow!

Saving design spins!

Will the IC Validator approach be able to save design spins? How much is the physical design cycle time reduced?

With the in-design physical verification, place-and-route engineers will be able to run sign-off quality DRC checks, timing aware and sign-off quality metal fill, all within the familiar IC Compiler environment. Linear scalability for efficient use of hardware, sign-off accuracy and integration with IC Compiler will enable productivity enhancing flows like auto detect and autofix, incremental verification flows -- all can significantly reduce time to tapeout.

How can it help in avoiding the painful sign-off failure-to-physical-redesign iterations that are increasingly common below 90nm?

With the seamless integration of the IC Validator with the IC Compiler, physical designers can now verify the design as they implement for manufacturing sign-off accuracy.

Incremental DRC's strength

How good is the incremental design-rule checker (DRC)? Is it really parallelized for the multicore servers?

According to Bali, incremental flows are one of the strongest tenants of IC Validator. To improve physical designer productivity, rule-based only or layer-based only incremental verification runs can be initiated from within IC Compiler.

He said: "For ECO validation, the IC Validator supports window or an area-based incremental verification approach to speed up surgical checks. The incremental flows are meant to be quick, but the IC Validator has multicore capability to further speed up the process."

The IC Validator discovers and fixes design rule violations within the global context of the design as well. How is this made possible?

With the in-design physical verification, the IC Validator can accurately and automatically identify DRC violation and automatically provide fix guidance to IC Compiler to fix the violation and then re-verify it again.

Handling metal fills and design changes

Operations typically performed during physical verification, such as metal fills, may trigger additional design changes to achieve timing closure. How is this handled by the IC Validator?

Bali said that the prevailing post-processing oriented DFM flows introduce excessive and lengthy discover-fix iterations. Metal fill insertion, a mandatory DFM step at the advanced nodes, exemplifies this issue.

"Physical designers stream out the timing closed post-fill design for signoff validation and then stream it back in to fix any signoff errors flagged during physical verification. This multi-hour discover-fix loop is typically repeated per block till the post-fill design is both signoff qualified and timing clean.

"With in-design physical verification, the IC Validator and IC Compiler address the challenges of DFM, within the place-and-route environment. The seamless integration enables a single pass metal fill flow that is timing aware and of signoff quality and is void of expensive streamouts and streamins," he added.

Said to provide a step up in physical designer productivity, it is architected to deliver the high accuracy necessary for leading-edge process nodes, superior scalability for efficient utilization of available hardware, and ease-of-use.

What does IC Validator do?

According to Sanjay Bali, Director of Marketing, Physical Verification & DFM, Synopsys, the IC Validator is a complete physical verification tool, performing increasingly complex DRC and LVS sign-off checks.

It has been specifically architected for in-design physical verification. This means: the place-and-route engineers can run DRC and practical DFM steps alongside place and route within the familiar IC Compiler physical design environment.

And, why need for such a solution? He added that three key summary challenges are driving the need for a new approach and hence the new tool. These are:

a) Increase in complexity and count of manufacturing rules.

b) Unabated growth on design complexity.

c) Increasing DFM challenges, which just cannot be handled in a post processing approach.

Currently, the solution is aimed at 45nm and below as these nodes largely represent the challenges listed above.

Enhancing physical designer's productivity

Three key tenants of the IC Validator that offer improved physical designer productivity are:

a) High accuracy necessary for leading-edge process nodes.

b) Superior scalability for efficient utilization of available hardware. And,

c) Ease of use with seamless integration of IC Validator and IC Compiler

Bali said: "The IC Validator has been architected from the ground up for in-design physical verification. In-design physical verification enables place-and-route engineers to accelerate the time to tapeout by enabling sign-off quality physical verification from within implementation or physical design. Physical designers designing with IC Compiler can now benefit from the in-design physical verification approach with the push of a button, incurring minimal overhead cost to eliminate surprises late in the design.

"With the verify-as-you-go approach replacing the implement-then-verify approach, physical designers can significantly reduce iteration count, eliminate streamouts and streamins, and accelerate time to tapeout. In addition, the integration enables several productivity enhancing flows like incremental DRC verification, incremental metal fill flows and ECO flows -- all leading to significant reduction in time to tapeout."

It would be interesting to determine or know by approximately what percent is the total physical verification time reduced, and what all does it cover in the process?

Bali added that in extreme cases, finding and fixing DRC violations can easily impact the schedules by a few weeks! The key here is that physical designers typically wait until the final stages of the tapeout to run physical verification. Inevitably, the schedule at this point is squeezed and the cost of fixing the error is high.

"With a sign-off quality physical verification tool integrated into the physical design environment, place-and-route engineers can verify as they implement and eliminate late surprises while speeding up the total physical verification turnaround time. In addition, the outcome of this process is a sign-off clean design.

Production ready!

The Synopsys IC Validator is also said to 'production ready!" What exactly does that mean?

The IC Validator has been successfully used to tapeout designs at several chip manufacturers, said Bali. In addition, it is currently being used for production designs at Nvidia and Toshiba. Besides other leading foundry's and chip manufactures it is also qualified by TSMC for 40nm and 28nm process nodes.

For those interested, Toshiba already has Synopsys as its key EDA partner, and NVIDIA adopted the IC Validator for sign-off physical verification, within days of its launch! More are bound to follow!

Saving design spins!

Will the IC Validator approach be able to save design spins? How much is the physical design cycle time reduced?

With the in-design physical verification, place-and-route engineers will be able to run sign-off quality DRC checks, timing aware and sign-off quality metal fill, all within the familiar IC Compiler environment. Linear scalability for efficient use of hardware, sign-off accuracy and integration with IC Compiler will enable productivity enhancing flows like auto detect and autofix, incremental verification flows -- all can significantly reduce time to tapeout.

How can it help in avoiding the painful sign-off failure-to-physical-redesign iterations that are increasingly common below 90nm?

With the seamless integration of the IC Validator with the IC Compiler, physical designers can now verify the design as they implement for manufacturing sign-off accuracy.

Incremental DRC's strength

How good is the incremental design-rule checker (DRC)? Is it really parallelized for the multicore servers?

According to Bali, incremental flows are one of the strongest tenants of IC Validator. To improve physical designer productivity, rule-based only or layer-based only incremental verification runs can be initiated from within IC Compiler.

He said: "For ECO validation, the IC Validator supports window or an area-based incremental verification approach to speed up surgical checks. The incremental flows are meant to be quick, but the IC Validator has multicore capability to further speed up the process."

The IC Validator discovers and fixes design rule violations within the global context of the design as well. How is this made possible?

With the in-design physical verification, the IC Validator can accurately and automatically identify DRC violation and automatically provide fix guidance to IC Compiler to fix the violation and then re-verify it again.

Handling metal fills and design changes

Operations typically performed during physical verification, such as metal fills, may trigger additional design changes to achieve timing closure. How is this handled by the IC Validator?

Bali said that the prevailing post-processing oriented DFM flows introduce excessive and lengthy discover-fix iterations. Metal fill insertion, a mandatory DFM step at the advanced nodes, exemplifies this issue.

"Physical designers stream out the timing closed post-fill design for signoff validation and then stream it back in to fix any signoff errors flagged during physical verification. This multi-hour discover-fix loop is typically repeated per block till the post-fill design is both signoff qualified and timing clean.

"With in-design physical verification, the IC Validator and IC Compiler address the challenges of DFM, within the place-and-route environment. The seamless integration enables a single pass metal fill flow that is timing aware and of signoff quality and is void of expensive streamouts and streamins," he added.

Labels:

DRC/LVS,

EDA,

EDA Tools,

IC validator,

physical designers,

Synopsys

NVIDIA deploys Magma Talus 1.1 into production

BANGALORE, INDIA: Magma Design Automation Inc. announced that NVIDIA Corp. deployed Magma’s Talus 1.1 IC implementation system into full production.

Talus 1.1 offers significant improvements in routing, optimization and runtime as well as enhanced usability features. NVIDIA had been participating in the beta testing of the latest Talus release and, based on the positive results of the testing and improved flow performance, made the decision to start using Talus 1.1 for NVIDIA’s production design projects.

“We have recently upgraded to Talus 1.1 in our production environment based on significant improvements in the core algorithms, flow convergence and the overall usability,” said Patrick Sproule, manager of VLSI Design for NVIDIA. “In particular, the improvements in runtime, timing convergence and ECO routing have improved our throughput and quality of results.”

Magma’s unified data model is a key factor in the performance of the Talus chip implementation system. All the implementation and analysis engines in the Talus flow are built around, and have access to, the same data, and as a result flow convergence and turnaround times are shortened and optimization steps can be applied across the flow.

“We made a significant R&D investment in Talus 1.1 with the focus on improving overall performance and convergence while also improving the ease-of-use and efficiency of the system,” said Premal Buch, general manager of Magma’s Design Implementation Business Unit.

“Our customers are implementing very complex chips and need the combination of a powerful, fast, high-quality chip design system that is also easy to drive. We made a specific effort in Talus 1.1 to develop simplified flows that reduce the number of commands required, but still deliver superior results in the finished design. We are very pleased with the fact that Talus 1.1 performed so well for NVIDIA that they have moved it onto their production chip design projects.”

Talus platform

Talus is a completely unified RTL-to-GDSII system for design implementation, with advanced capabilities for nanometer design. To address shorter time-to-market windows, Talus is the first implementation solution to multi-process the entire IC design flow. Its front-end design system provides logic designers with a fast, high-capacity, physically aware synthesis capability.

Its physical design system addresses variability and multimode/multicorner complexity with new optimization, place and route, and clock tree synthesis technology. To reduce leakage and dynamic power, Talus also provides a complete low-power design system. To improve manufacturability and reliability, Talus provides built-in design-for-manufacturing (DFM) features such as redundant via insertion, recommended end-of-line extension, and wire spreading & widening.

Talus 1.1 offers significant improvements in routing, optimization and runtime as well as enhanced usability features. NVIDIA had been participating in the beta testing of the latest Talus release and, based on the positive results of the testing and improved flow performance, made the decision to start using Talus 1.1 for NVIDIA’s production design projects.

“We have recently upgraded to Talus 1.1 in our production environment based on significant improvements in the core algorithms, flow convergence and the overall usability,” said Patrick Sproule, manager of VLSI Design for NVIDIA. “In particular, the improvements in runtime, timing convergence and ECO routing have improved our throughput and quality of results.”

Magma’s unified data model is a key factor in the performance of the Talus chip implementation system. All the implementation and analysis engines in the Talus flow are built around, and have access to, the same data, and as a result flow convergence and turnaround times are shortened and optimization steps can be applied across the flow.

“We made a significant R&D investment in Talus 1.1 with the focus on improving overall performance and convergence while also improving the ease-of-use and efficiency of the system,” said Premal Buch, general manager of Magma’s Design Implementation Business Unit.

“Our customers are implementing very complex chips and need the combination of a powerful, fast, high-quality chip design system that is also easy to drive. We made a specific effort in Talus 1.1 to develop simplified flows that reduce the number of commands required, but still deliver superior results in the finished design. We are very pleased with the fact that Talus 1.1 performed so well for NVIDIA that they have moved it onto their production chip design projects.”

Talus platform

Talus is a completely unified RTL-to-GDSII system for design implementation, with advanced capabilities for nanometer design. To address shorter time-to-market windows, Talus is the first implementation solution to multi-process the entire IC design flow. Its front-end design system provides logic designers with a fast, high-capacity, physically aware synthesis capability.

Its physical design system addresses variability and multimode/multicorner complexity with new optimization, place and route, and clock tree synthesis technology. To reduce leakage and dynamic power, Talus also provides a complete low-power design system. To improve manufacturability and reliability, Talus provides built-in design-for-manufacturing (DFM) features such as redundant via insertion, recommended end-of-line extension, and wire spreading & widening.

LG selects Cypress' CapSense for LCD monitors

SAN JOSE, USA: Cypress Semiconductor Corp. today announced that LG Electronics has selected its CapSense touch-sensing solution to implement the stylish user interface in the new W53 and W54 LCD monitors.

Using CapSense proximity-sensing, the monitors feature a clean, black bezel with control buttons that only illuminate when a user’s finger approaches. LG designers leveraged the flexibility of the PSoC programmable SoC architecture to implement LED animation control, I2C sensitivity control and other functions beyond touch sensing - a capability called CapSense Plus -- in the W53, W54 and other LCD monitors, as well as in the Scarlet II LCD TV line.

Using CapSense proximity-sensing, the monitors feature a clean, black bezel with control buttons that only illuminate when a user’s finger approaches. LG designers leveraged the flexibility of the PSoC programmable SoC architecture to implement LED animation control, I2C sensitivity control and other functions beyond touch sensing - a capability called CapSense Plus -- in the W53, W54 and other LCD monitors, as well as in the Scarlet II LCD TV line.

Cypress is the industry touch-sensing leader, with over 3 billion mechanical buttons replaced in mobile handsets, laptops, consumer electronics, white goods, automotive applications and more. LG has selected the CapSense solution for mobile handsets, air cleaners and other products in addition to LCD monitors and televisions.

LG’s W53 and W54 SMART Monitor Series offer top picture quality while greatly reducing eyestrain during extended use. These monitors include an Auto Brightness feature that allows them to automatically optimize their brightness and other picture settings based on the ambient light in the room and the content being viewed. The W53 and W54 monitors are available in sizes from 18.5 to 27 inches.

“CapSense enables compelling touch-sensing interfaces, and the integration of proximity sensing contributes to the unique design of our LCD Monitors,” said JunHo Shin, engineer for Business Solutions R&D at LG. “Equally as important, CapSense delivers well-established quality from the industry leader in touch-sensing technology.”

“Winning an initial design with a leading provider of elegant consumer electronics such as LG points to the innovative touch-sensing interfaces the CapSense solution enables,” said Dhwani Vyas, vice president of the User Interface Business Unit at Cypress. “Having LG select CapSense across multiple product lines is excellent validation of its flexibility, ease-of-use and reliability.”

Cypress is the industry touch-sensing leader, with over 3 billion mechanical buttons replaced in mobile handsets, laptops, consumer electronics, white goods, automotive applications and more. LG has selected the CapSense solution for mobile handsets, air cleaners and other products in addition to LCD monitors and televisions.

LG’s W53 and W54 SMART Monitor Series offer top picture quality while greatly reducing eyestrain during extended use. These monitors include an Auto Brightness feature that allows them to automatically optimize their brightness and other picture settings based on the ambient light in the room and the content being viewed. The W53 and W54 monitors are available in sizes from 18.5 to 27 inches.

“CapSense enables compelling touch-sensing interfaces, and the integration of proximity sensing contributes to the unique design of our LCD Monitors,” said JunHo Shin, engineer for Business Solutions R&D at LG. “Equally as important, CapSense delivers well-established quality from the industry leader in touch-sensing technology.”

“Winning an initial design with a leading provider of elegant consumer electronics such as LG points to the innovative touch-sensing interfaces the CapSense solution enables,” said Dhwani Vyas, vice president of the User Interface Business Unit at Cypress. “Having LG select CapSense across multiple product lines is excellent validation of its flexibility, ease-of-use and reliability.”

MEMS inertial sensors market: Business potential and key challenges

LYON, FRANCE: Yole Développement has released its new report dedicated to MEMS accelerometers, gyroscopes and IMU Market from 2008 to 2013. The French consulting company has presented its marketing and technological analysis on MEMS inertial market with a strong focus on the consumer market.

How is the consumer electronics changing the MEMS motion sensor industry? Does the Automotive market affect the MEMS Inertial suppliers? Yole updated its figures, marketing and technological trends. And for the second time, the market analysts are giving today its expertise on the market, which is the one of the most important in the MEMS industry.

Motion sensing devices are not new. They have been used since the 50s in aerospace and defense fields for navigation functions. MEMS versions of accelerometers and gyroscopes have only been developed more recently, bringing two key advantages: cost and size reduction.

While not as accurate as the devices used for military applications, MEMS‐type accelerometers and gyroscopes are well adapted to be integrated into cars and many consumer electronic products. MEMS accelerometers have been extensively used since the 90s in light vehicle airbags, as crash sensors.

Since then many other devices have benefited from the use of motion sensors. The latest and most striking examples are their use in Nintendo Wii game controllers and in Apple iPhone and iPod devices. Source: Yole Développement

Source: Yole Développement

MEMS accelerometers and gyroscopes: already a 1.80B$ market in 2008

MEMS inertial sensors now represent a serious business: “752M units of MEMS accelerometers and gyroscopes were produced worldwide in 2008, corresponding to a 1.80B$ market already”, says Laurent Robin, MEMS Market Analyst at Yole. “The major part of this market still comes from automotive applications; however consumer applications should overtake this by 2011”, explains Laurent.

This is not only due to the current downturn which is impacting the automotive world: massive use of accelerometer and gyroscope is likely to stay limited to current established applications such as airbag, ESC and TPMS.

The annual growth rate will be limited to 3.6 percent up to 2013, compared to 21.1 percent for the consumer area. Indeed, the adoption rate of motion sensors on many consumer electronics products is rising faster than ever.

For example, Bosch (including its Sensortec division) and ST Microelectronics are leading the global MEMS accelerometer market with about 35 percent of market share together. Indeed, STM has recently benefited from key contracts such as the one with Apple. Its main challengers are ADI, Freescale, VTI and Infineon, and new players continue to enter the market.

From the gyroscope side, three players dominated the market in 2008: Bosch, Systron Donner and Panasonic had, on average, 20 percent market share each. However the automotive part of Systron Donner shut down in the beginning of 2009, which is greatly impacting the automotive electronics field.

Cost and intelligence are driving development of future product generations

Successful MEMS providers will be the ones able to deal with this changing economic landscape.

Some devices now integrate MEMS sensors as a commodity product. In other cases, integration of MEMS is driven by regulation and the user is not willing to pay a price premium for additional sensors. Pressure on cost is thus enormous in the last two cases. Successful players are the ones able to decrease manufacturing costs.

One strategy is to produce on 8” infrastructure. This has been chosen by several players: ST Microelectronics, Bosch Sensortec (Fab is ready, but not in use yet), Freescale, TSMC (foundry service).

Other players have moved to a technology renowned to be more able to handle cost reduction. A nice example is Panasonic which has successfully moved its gyroscope production from quartz to silicon substrates.

When it comes to very high volumes, big IC players are often preferred. Besides been able to sustain high price pressure, they are used to delivering very reliable products, to managing efficiently the supply chain and to ramping up production easily.

Being able to add intelligence to the sensor is also a means to offer strong product differentiators. From supplying only a component, many players are now supplying a solution. Algorithms are commonly integrated at the chip level: for screen rotation, drop detection… This is why a company such as Kionix has been successful in the HDD protection market: notebook free‐fall scenarios have been successfully implemented.

Providing software and system development around the sensor is also essential. It is thus not surprising that in many companies today, more people are working on the software side than on the process side!

MEMS Inertial Sensors Market 2009 Report will be available in June 2009, The catalog price: EURO 3,990 (single user license).

How is the consumer electronics changing the MEMS motion sensor industry? Does the Automotive market affect the MEMS Inertial suppliers? Yole updated its figures, marketing and technological trends. And for the second time, the market analysts are giving today its expertise on the market, which is the one of the most important in the MEMS industry.

Motion sensing devices are not new. They have been used since the 50s in aerospace and defense fields for navigation functions. MEMS versions of accelerometers and gyroscopes have only been developed more recently, bringing two key advantages: cost and size reduction.

While not as accurate as the devices used for military applications, MEMS‐type accelerometers and gyroscopes are well adapted to be integrated into cars and many consumer electronic products. MEMS accelerometers have been extensively used since the 90s in light vehicle airbags, as crash sensors.

Since then many other devices have benefited from the use of motion sensors. The latest and most striking examples are their use in Nintendo Wii game controllers and in Apple iPhone and iPod devices.

MEMS accelerometers and gyroscopes: already a 1.80B$ market in 2008

MEMS inertial sensors now represent a serious business: “752M units of MEMS accelerometers and gyroscopes were produced worldwide in 2008, corresponding to a 1.80B$ market already”, says Laurent Robin, MEMS Market Analyst at Yole. “The major part of this market still comes from automotive applications; however consumer applications should overtake this by 2011”, explains Laurent.

This is not only due to the current downturn which is impacting the automotive world: massive use of accelerometer and gyroscope is likely to stay limited to current established applications such as airbag, ESC and TPMS.

The annual growth rate will be limited to 3.6 percent up to 2013, compared to 21.1 percent for the consumer area. Indeed, the adoption rate of motion sensors on many consumer electronics products is rising faster than ever.

For example, Bosch (including its Sensortec division) and ST Microelectronics are leading the global MEMS accelerometer market with about 35 percent of market share together. Indeed, STM has recently benefited from key contracts such as the one with Apple. Its main challengers are ADI, Freescale, VTI and Infineon, and new players continue to enter the market.

From the gyroscope side, three players dominated the market in 2008: Bosch, Systron Donner and Panasonic had, on average, 20 percent market share each. However the automotive part of Systron Donner shut down in the beginning of 2009, which is greatly impacting the automotive electronics field.

Cost and intelligence are driving development of future product generations

Successful MEMS providers will be the ones able to deal with this changing economic landscape.

Some devices now integrate MEMS sensors as a commodity product. In other cases, integration of MEMS is driven by regulation and the user is not willing to pay a price premium for additional sensors. Pressure on cost is thus enormous in the last two cases. Successful players are the ones able to decrease manufacturing costs.

One strategy is to produce on 8” infrastructure. This has been chosen by several players: ST Microelectronics, Bosch Sensortec (Fab is ready, but not in use yet), Freescale, TSMC (foundry service).

Other players have moved to a technology renowned to be more able to handle cost reduction. A nice example is Panasonic which has successfully moved its gyroscope production from quartz to silicon substrates.

When it comes to very high volumes, big IC players are often preferred. Besides been able to sustain high price pressure, they are used to delivering very reliable products, to managing efficiently the supply chain and to ramping up production easily.

Being able to add intelligence to the sensor is also a means to offer strong product differentiators. From supplying only a component, many players are now supplying a solution. Algorithms are commonly integrated at the chip level: for screen rotation, drop detection… This is why a company such as Kionix has been successful in the HDD protection market: notebook free‐fall scenarios have been successfully implemented.

Providing software and system development around the sensor is also essential. It is thus not surprising that in many companies today, more people are working on the software side than on the process side!

MEMS Inertial Sensors Market 2009 Report will be available in June 2009, The catalog price: EURO 3,990 (single user license).

Labels:

gyroscopes,

IMU,

MEMS,

MEMS accelerometers,

Yole Développement

Investment in Taiwan will help fix Mainland China's broken IC industry

NEW TRIPOLI, USA: Mainland China’s cross-straits investment in Taiwan will help the island country to survive the global crisis and at the same time help fix its own IC market, according to the report “Mainland China’s Semiconductor and Equipment Markets,” recently published by The Information Network.

“China’s chip industry is broken, a combination of the recession and too little money being spent by the government. Only $7 billion was spent on fabs in the past five years, enough to build only two 300mm fabs,” says Dr. Robert Castellano, President of The Information Network. “Investments by China into Taiwan will not only enable the country to endure its deepest recession, which was down 10.24% last quarter, but will catalyze a change in the Taiwanese government’s attitude toward semiconductor technology transfer.”

For years, rigid regulations controlled technology and monetary outflows from Taiwanese chip makers to China. Several factors played a role, such as concerns about China stealing and copying IP, fear that the technology would strengthen China’s military capabilities, and loss of jobs.

“Macroeconomic forces have changed the landscape. Taiwan needs money, and although the government may be reticent to give up its advanced technology, China’s massive economic stimulus package to Taiwan will serve to lessen regulations,” added Dr. Castellano. “This move will strengthen China’s semiconductor companies, minimizing the need to import the vast number of chips it currently does to manufacture consumer electronic products.”

China's IC industry is expanding rapidly. In 2008 Mainland China produced 42.5 billion ICs, which accounted for 24.3 percent of domestic demand as a result of massive building programs and the weak economy. In comparison, Mainland China produced only 20.9 percent five years ago. However, in 2008, consumption of ICs in Mainland China is outpaced production in domestically made ICs. Consumption grew 6.8 percent to 174.7 billion chips while production decreased 0.4 percent to 42.5 billion chips.

However, in 2008, consumption of ICs in Mainland China is outpaced production in domestically made ICs. Consumption grew 6.8 percent to 174.7 billion chips while production decreased 0.4 percent to 42.5 billion chips.

These issues are resulting in consolidation as the mainly foundry-based Chinese industry (SMIC, Grace, HeJian, ASMC, and CR Micro) competes with TSMC, UMC, and other entrenched Asian foundries. Hua Hong NEC Electronics will soon acquire Grace Semiconductor.

Things are also changing internally in China. As much as $25 billion is earmarked over the next five years to prop up the industry, including $5 billion for the joint venture between Elpida and Suzhou Venture Group and $5 billion for Sino-chip.

“Areas propelling the Chinese IC industry are part of the government stimulus program such as projects to supply subsidized electronic goods to rural areas of China. The construction of 3G networks, the expansion of mobile TV operations are big areas of opportunity,” added Dr. Castellano. “The Chinese government has realized internal stimulus was not enough without the advanced technology needed from Taiwan to make these programs successful.”

“China’s chip industry is broken, a combination of the recession and too little money being spent by the government. Only $7 billion was spent on fabs in the past five years, enough to build only two 300mm fabs,” says Dr. Robert Castellano, President of The Information Network. “Investments by China into Taiwan will not only enable the country to endure its deepest recession, which was down 10.24% last quarter, but will catalyze a change in the Taiwanese government’s attitude toward semiconductor technology transfer.”

For years, rigid regulations controlled technology and monetary outflows from Taiwanese chip makers to China. Several factors played a role, such as concerns about China stealing and copying IP, fear that the technology would strengthen China’s military capabilities, and loss of jobs.

“Macroeconomic forces have changed the landscape. Taiwan needs money, and although the government may be reticent to give up its advanced technology, China’s massive economic stimulus package to Taiwan will serve to lessen regulations,” added Dr. Castellano. “This move will strengthen China’s semiconductor companies, minimizing the need to import the vast number of chips it currently does to manufacture consumer electronic products.”

China's IC industry is expanding rapidly. In 2008 Mainland China produced 42.5 billion ICs, which accounted for 24.3 percent of domestic demand as a result of massive building programs and the weak economy. In comparison, Mainland China produced only 20.9 percent five years ago.

However, in 2008, consumption of ICs in Mainland China is outpaced production in domestically made ICs. Consumption grew 6.8 percent to 174.7 billion chips while production decreased 0.4 percent to 42.5 billion chips.

However, in 2008, consumption of ICs in Mainland China is outpaced production in domestically made ICs. Consumption grew 6.8 percent to 174.7 billion chips while production decreased 0.4 percent to 42.5 billion chips.These issues are resulting in consolidation as the mainly foundry-based Chinese industry (SMIC, Grace, HeJian, ASMC, and CR Micro) competes with TSMC, UMC, and other entrenched Asian foundries. Hua Hong NEC Electronics will soon acquire Grace Semiconductor.

Things are also changing internally in China. As much as $25 billion is earmarked over the next five years to prop up the industry, including $5 billion for the joint venture between Elpida and Suzhou Venture Group and $5 billion for Sino-chip.

“Areas propelling the Chinese IC industry are part of the government stimulus program such as projects to supply subsidized electronic goods to rural areas of China. The construction of 3G networks, the expansion of mobile TV operations are big areas of opportunity,” added Dr. Castellano. “The Chinese government has realized internal stimulus was not enough without the advanced technology needed from Taiwan to make these programs successful.”

Labels:

ASMC,

China,

China's IC market trends,

CR Micro,

Grace,

HeJian,

IC indusrty,

MIC,

The Information Network

Novellus HCM IONX XL Ta(N) barrier technology enables 3X/2Xnm memory transition to copper

SAN JOSE: Ten years after the introduction of copper metallization for logic device manufacturing, Physical Vapor Deposition (PVD) copper barrier-seed and copper electrochemical deposition (ECD) are now being used for the production of DRAM and Flash memory chips. The memory transition from aluminum metallization to copper interconnects is being driven by the technological challenges associated with device scaling and the need to reduce memory chip manufacturing cost.

One of the key components of a copper memory interconnect is the PVD tantalum nitride (Ta(N)) barrier layer that provides the necessary copper diffusion resistance, as well as wettability for the subsequent copper seed layer. For memory manufacturers, the challenge comes with depositing this barrier film in advanced device structures that can possess up to 30 percent smaller critical dimensions (CD) than those found in logic applications.

For these aggressive geometries, planar PVD is limited by shadowing effects that can cause incomplete film coverage due to overhang at the top corner of the trench or via, in turn leading to inadequate copper fill and yield loss. Some planar PVD barrier solutions are investigating the incorporation of more expensive CVD layers to mitigate these effects. Compounding these challenges is the fact that Ta(N) barriers also need to be very thin (less than 120Å in the field) in order to minimize the volume fraction of high resistivity Ta(N) relative to low resistivity copper within the feature.

To address the challenges discussed above, Novellus has developed the IONX XL (eXtended Life) Ta(N) barrier process for the 3x/2xnm memory node, based on Novellus' PVD Hollow Cathode Magnetron (HCM) deposition technology. This PVD-only barrier process deposits high quality films with excellent step coverage for high aspect ratio memory structures.

The conformal Ta(N) films deposited with this technology are the result of an increased plasma density and more effective control of the ionized flux that reaches the wafer surface. A thin, highly conformal IONX XL Ta(N) barrier layer is deposited into a 3xnm memory device trench with no top corner overhang.

Not only does this robust copper barrier process meet the technical challenges of advanced memory, but it also results in a 40 percent reduction in the tantalum Cost of Consumables (CoC) compared to competitive market offerings. A 100,000 wafer-starts-per-month memory megafab using two levels of metal can save approximately $1M a year in consumable costs through more efficient utilization of the tantalum target material.

"As memory technology transitions to copper interconnects, the 3x/2xnm device dimensions are placing stringent technical and cost requirements on the Ta(N) barrier layer," said Dr. Wai-Fan Yau, general manager for Novellus' Integrated Metals Business Unit. "The new IONX XL barrier film meets these advanced technical demands and also provides a significant reduction in consumable costs."

One of the key components of a copper memory interconnect is the PVD tantalum nitride (Ta(N)) barrier layer that provides the necessary copper diffusion resistance, as well as wettability for the subsequent copper seed layer. For memory manufacturers, the challenge comes with depositing this barrier film in advanced device structures that can possess up to 30 percent smaller critical dimensions (CD) than those found in logic applications.

For these aggressive geometries, planar PVD is limited by shadowing effects that can cause incomplete film coverage due to overhang at the top corner of the trench or via, in turn leading to inadequate copper fill and yield loss. Some planar PVD barrier solutions are investigating the incorporation of more expensive CVD layers to mitigate these effects. Compounding these challenges is the fact that Ta(N) barriers also need to be very thin (less than 120Å in the field) in order to minimize the volume fraction of high resistivity Ta(N) relative to low resistivity copper within the feature.

To address the challenges discussed above, Novellus has developed the IONX XL (eXtended Life) Ta(N) barrier process for the 3x/2xnm memory node, based on Novellus' PVD Hollow Cathode Magnetron (HCM) deposition technology. This PVD-only barrier process deposits high quality films with excellent step coverage for high aspect ratio memory structures.

The conformal Ta(N) films deposited with this technology are the result of an increased plasma density and more effective control of the ionized flux that reaches the wafer surface. A thin, highly conformal IONX XL Ta(N) barrier layer is deposited into a 3xnm memory device trench with no top corner overhang.

Not only does this robust copper barrier process meet the technical challenges of advanced memory, but it also results in a 40 percent reduction in the tantalum Cost of Consumables (CoC) compared to competitive market offerings. A 100,000 wafer-starts-per-month memory megafab using two levels of metal can save approximately $1M a year in consumable costs through more efficient utilization of the tantalum target material.

"As memory technology transitions to copper interconnects, the 3x/2xnm device dimensions are placing stringent technical and cost requirements on the Ta(N) barrier layer," said Dr. Wai-Fan Yau, general manager for Novellus' Integrated Metals Business Unit. "The new IONX XL barrier film meets these advanced technical demands and also provides a significant reduction in consumable costs."

Global semicon revenue to decline 22 percent in 2009

STAMFORD, USA: Worldwide semiconductor revenue is forecast to reach $198 billion in 2009, a 22.4 percent decline from 2008 revenue of $255 billion, according to the latest projections by Gartner Inc.

This outlook is slightly better than the first quarter projections, when Gartner forecast semiconductor revenue to decline 24.1 percent in 2009.

"First quarter PC shipments came in better than expected, which led to an improved outlook for microprocessors, but we believe most of this improvement was due to the fact that inventories had been run down too far, rather than true demand returning," said Bryan Lewis, research vice president at Gartner.

"We are expecting 4.9 percent growth in second quarter semiconductor sales based on recent semiconductor company guidance, and this positive movement has caused us to move away from our 1Q09 worst-case scenario of a record down year in 2009. While this is positive news, the semiconductor industry is clearly not out of the woods, as there is minimal evidence that demand is returning, except in China," Lewis said.

Inventory burn in the PC market in the fourth quarter of 2008 and in January and February 2009 pushed component demand significantly below PC demand, driving down prices across the board.

Gartner analysts said PC vendors that started cutting inventory early were able to achieve significant savings on bill of materials. As the inventory correction swings in the opposite direction, Gartner expects component prices to stabilize through the year.

Application-specific standard product (ASSP) will continue to lead semiconductor revenue, as it is forecast to total $51.9 billion in 2009, a 24.2 percent decline from 2008. The memory market will be the No. 2 segment for the semiconductor industry, as it totals $39.4 billion, a 16.8 percent decline from 2008.

The microcomponents segment (microprocessors, micro controller units, digital signal processors) will drop from the No. 2 spot in 2008 to the No. 3 spot in 2009. Microcomponents are projected to reach $37.3 billion, a 23.6 percent decline from 2008.

"Consumer spending will remain somewhat depressed due to high unemployment, low housing pricing, and relatively low consumer confidence," Lewis said. "IT budgets are modestly down in 2009, but companies are not spending at the rate of their budgets."

Gartner has removed solar revenue from its semiconductor forecast because solar cells are not traditional semiconductor devices (solar cells focus on energy generation and are not components in an electronic system), and their high growth rates were distorting the true growth of the semiconductor industry. Gartner is expanding its coverage in solar and will provide detailed technology forecast breakouts in separate reports.

This outlook is slightly better than the first quarter projections, when Gartner forecast semiconductor revenue to decline 24.1 percent in 2009.

"First quarter PC shipments came in better than expected, which led to an improved outlook for microprocessors, but we believe most of this improvement was due to the fact that inventories had been run down too far, rather than true demand returning," said Bryan Lewis, research vice president at Gartner.

"We are expecting 4.9 percent growth in second quarter semiconductor sales based on recent semiconductor company guidance, and this positive movement has caused us to move away from our 1Q09 worst-case scenario of a record down year in 2009. While this is positive news, the semiconductor industry is clearly not out of the woods, as there is minimal evidence that demand is returning, except in China," Lewis said.

Inventory burn in the PC market in the fourth quarter of 2008 and in January and February 2009 pushed component demand significantly below PC demand, driving down prices across the board.

Gartner analysts said PC vendors that started cutting inventory early were able to achieve significant savings on bill of materials. As the inventory correction swings in the opposite direction, Gartner expects component prices to stabilize through the year.

Application-specific standard product (ASSP) will continue to lead semiconductor revenue, as it is forecast to total $51.9 billion in 2009, a 24.2 percent decline from 2008. The memory market will be the No. 2 segment for the semiconductor industry, as it totals $39.4 billion, a 16.8 percent decline from 2008.

The microcomponents segment (microprocessors, micro controller units, digital signal processors) will drop from the No. 2 spot in 2008 to the No. 3 spot in 2009. Microcomponents are projected to reach $37.3 billion, a 23.6 percent decline from 2008.

"Consumer spending will remain somewhat depressed due to high unemployment, low housing pricing, and relatively low consumer confidence," Lewis said. "IT budgets are modestly down in 2009, but companies are not spending at the rate of their budgets."

Gartner has removed solar revenue from its semiconductor forecast because solar cells are not traditional semiconductor devices (solar cells focus on energy generation and are not components in an electronic system), and their high growth rates were distorting the true growth of the semiconductor industry. Gartner is expanding its coverage in solar and will provide detailed technology forecast breakouts in separate reports.

2H May mainstream NAND Flash MLC average contract price slightly declined 2-6pc

TAIPEI, TAIWAN: NAND Flash contract price remains flat in 2H May. Some mainstream MLC average contract price has slightly declined 2 percent to 6 percent due to the high density products promotion by some vendors in Mid-May,says DRAMeXchange.

Fig.1: 32Gb MLC NAND Flash Contract Price trend With the coming quarter end, some vendors already initiated the promotion programs to lower their inventory level. High density NAND Flash MLC chips under new process technology have comparably favor discount than those low density chips under more mature process technology.

With the coming quarter end, some vendors already initiated the promotion programs to lower their inventory level. High density NAND Flash MLC chips under new process technology have comparably favor discount than those low density chips under more mature process technology.

Therefore, the decline degree of the contract price “Low” for 32Gb MLC NAND Flash is larger than other NAND Flash chips in 2HMay. Meanwhile, some vendors keep making effort on the contract price stabilization to improve profitability since they still treat system maker customers as the shipment priority and result in the flat contract price “High” of 32Gb MLC NAND Flash in 2HMay.According to DRAMeXchange.

As for the demand side, DRAMeXchange states that May and June are perceived as the slow seasons for NAND Flash end products such as memory card and UFD. Some downstream clients are expecting for lower chip price for the sake of promotion in summer break.

Fig. 2: 32Gb MLC NAND Flash Spot Price trend However, the 2Q09 profitability has turned to the first priority of the suppliers and stable chip price in June is the clearly intension. The mindset difference toward future price between buyers and suppliers has resulted in the recent fluctuation and consolidation in spot market.

However, the 2Q09 profitability has turned to the first priority of the suppliers and stable chip price in June is the clearly intension. The mindset difference toward future price between buyers and suppliers has resulted in the recent fluctuation and consolidation in spot market.

The June contract price is likely to remain flat or might slightly soften due to the tug-of-war status between both sides.

Fig.1: 32Gb MLC NAND Flash Contract Price trend

With the coming quarter end, some vendors already initiated the promotion programs to lower their inventory level. High density NAND Flash MLC chips under new process technology have comparably favor discount than those low density chips under more mature process technology.

With the coming quarter end, some vendors already initiated the promotion programs to lower their inventory level. High density NAND Flash MLC chips under new process technology have comparably favor discount than those low density chips under more mature process technology.Therefore, the decline degree of the contract price “Low” for 32Gb MLC NAND Flash is larger than other NAND Flash chips in 2HMay. Meanwhile, some vendors keep making effort on the contract price stabilization to improve profitability since they still treat system maker customers as the shipment priority and result in the flat contract price “High” of 32Gb MLC NAND Flash in 2HMay.According to DRAMeXchange.

As for the demand side, DRAMeXchange states that May and June are perceived as the slow seasons for NAND Flash end products such as memory card and UFD. Some downstream clients are expecting for lower chip price for the sake of promotion in summer break.

Fig. 2: 32Gb MLC NAND Flash Spot Price trend

However, the 2Q09 profitability has turned to the first priority of the suppliers and stable chip price in June is the clearly intension. The mindset difference toward future price between buyers and suppliers has resulted in the recent fluctuation and consolidation in spot market.

However, the 2Q09 profitability has turned to the first priority of the suppliers and stable chip price in June is the clearly intension. The mindset difference toward future price between buyers and suppliers has resulted in the recent fluctuation and consolidation in spot market. The June contract price is likely to remain flat or might slightly soften due to the tug-of-war status between both sides.

Labels:

DRAM,

DRAMeXchange,

MLC NAND Flash contract price

Netronome licenses ARM multicore processor for next-gen network flow processors

CAMBRIDGE, UK: ARM announced that Netronome, a leading developer of highly programmable semiconductor products that provide intelligent and secure flow processing for virtualized servers and network equipment, has licensed the ARM11 MPCore multicore processor and a portfolio of ARM Physical IP for incorporation into its NFP-32xx family of Network Flow Processors.

Netronome’s network flow processors (NFPs) incorporate a high-performance, parallel processing architecture to enable wire-speed processing of complex Layer 2-7 algorithms, security processing, deep packet inspection and filtering, traffic management and forwarding applications.

By integrating capabilities that have typically required multiple specialized processors, Netronome NFPs provide a cost-effective, low power platform for a broad range of emerging applications requiring high-performance packet and content processing with robust security features, including switching and routing, network security, broadband access, test and measurement and wireless markets.

The NFP-32xx family of devices extends the performance and application reach of the family of Intel® IXP28xx products licensed by Netronome in November 2007, while preserving the software compatibility with existing IXP28xx devices.

Appropriate telecom and enterprise applications include line cards and standalone communications appliances that perform tasks such as protocol interworking, MAC emulation, Ethernet switching and IPv4/IPv6 forwarding. This is critical in enabling OEMs to deliver new line card functionality and services, while minimizing development time and cost.

In designs based on the NFP, the ARM11 MPCore processor can be used to process complex algorithms, maintain route tables, manage system level functions and perform control plane tasks.

Devices containing the ARM11 MPCore processor can be configured to contain between one and four processors delivering up to an aggregate 5000 Dhrystone MIPS of performance at 1GHz. By providing a scalable solution, the ARM11 MPCore processor enables existing software portability across single CPU and multi-CPU designs.

In addition to the ARM11 MPCore processor, Netronome incorporated ARM High Speed Interface IP in their design. ARM High Speed Interface IP delivers physical interface and analog timing solutions for a broad range of SDRAM DDR (double-data rate) applications ranging from high-speed mission critical applications to low-power memory sub-systems.

These silicon-proven solutions have been optimized for high data bandwidth, lowest power and enhanced signaling integrity features to enable support for a wide range of applications from high-end graphics, high-speed communications to low-power handheld devices.

ARM’s ability to deliver processor IP and physical IP in parallel ensures complete integration of complementary IP enabling the development of performance driven consumer devices requiring advanced functionality without increasing power consumption.

“Our analysis has shown that the use of multicore technology is the most power efficient way to scale wire-speed performance,” said Jim Finnegan, senior vice president of silicon engineering at Netronome. “Having a range of network processor solution options, with architecture compatibility across the entire family of Netronome devices enables our customers to maximize their software investment.”

“The efforts of Partners such as Netronome have helped to increase the ARM architecture’s presence in the networking market. This in turn has driven an ecosystem of optimized software and tools to enable innovative new applications,” said Ian Ferguson, director, Enterprise Solutions, ARM. “With current concerns about energy efficiency and utilization, the ability to perform wire-speed processing inside the power envelope associated with mobile platforms offers significant opportunities for OEM differentiation.”